# 73K224BL V.22bis, V.22, V.21, Bell 212A, 103 Single-Chip Modem w/ Integrated Hybrid

Simplifying System Integration™

# DATA SHEET

# DESCRIPTION

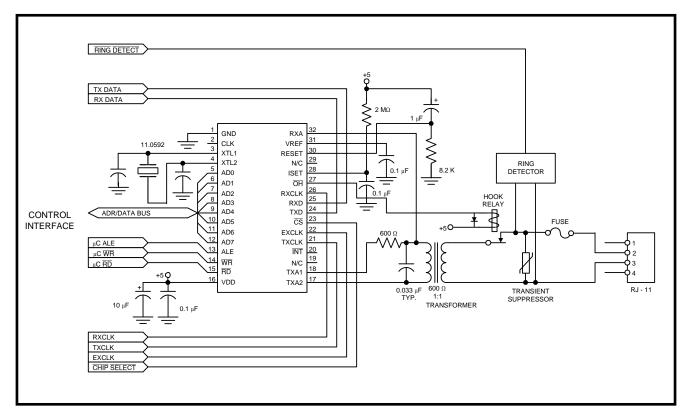

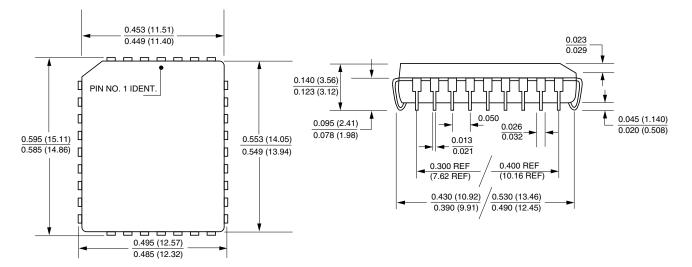

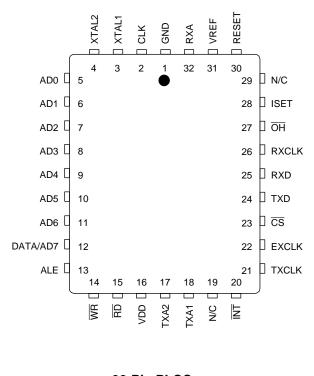

The 73K224BL is a highly integrated single-chip modem IC which provides the functions needed to construct a V.22bis compatible modem, capable of 2400 bit/s full-duplex operation over dial-up lines. The 73K224BL is an enhancement of the 73K224L single-chip modem, which adds the hybrid hook switch control, and driver to the 73K224L. The 73K224BL integrates analog, digital, and switched-capacitor array functions on a single chip, offering excellent performance and a high level of functional integration in a 32-Lead PLCC package.

The 73K224BL operates from a single +5 V supply for low power consumption.

The 73K224BL is designed to appear to the systems designer as a microprocessor peripheral, and will easily interface with popular single-chip microprocessors (80C51 typical) for control of modem functions through its 8-bit multiplexed address/data bus or via an optional serial control bus. An ALE control simplifies address demultiplexing. Data communications normally occur through a separate serial port.

(continued)

## FEATURES

- Includes features of 73K224L single-chip modem

- On chip 2-wire/4-wire hybrid driver and off hook relay buffer driver

- One-chip multi-mode V.22bis/V.22/V.21 and Bell 212A/103 compatible modem data pump

- FSK (300 bit/s), DPSK (600, 1200 bit/s), or QAM (2400 bit/s) encoding

- Software compatible with other TERIDIAN Semiconductor K-Series one-chip modems

- Interfaces directly with standard microprocessors (80C51 typical)

- Parallel or serial bus for control

- Selectable internal buffer/debuffer and scrambler/descrambler functions

- All asynchronous and synchronous operating modes (internal, external, slave)

(continued)

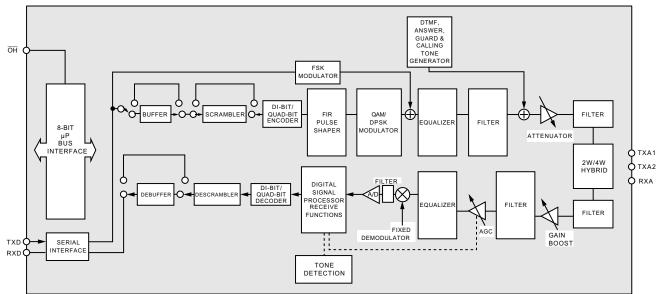

# BLOCK DIAGRAM

## **DESCRIPTION** (continued)

The 73K224BL is pin and software compatible with the 73K222BL, allowing system upgrades with a single component change.

The 73K224BL is designed to be a complete V.22bis compatible modem on a chip. The complete modem requires only the addition of the phone line interface, a control microprocessor, and RS-232 level converter for a typical system. Many functions were included to simplify implementation of typical modem designs. In addition to the basic 2400 bit/s QAM. 600/1200 bit/s DPSK and 300 bit/s FSK modulator/demodulator sections, the device also synch/asynch converters. includes scrambler/descrambler, call progress tone detect, DTMF tone generator capabilities and handshake pattern detectors. Test features such as analog loop, digital loop, and remote digital loopback are supported. Internal pattern generators are also included for self-testing.

## FEATURES (continued)

- Adaptive equalization for optimum performance over all lines

- Programmable transmit attenuation (16 dB, 1 dB steps), selectable receive boost (+18 dB)

- Call progress, carrier, answer tone, unscrambled mark, S1, and signal quality monitors

- DTMF, answer and guard tone generators

- Test modes available: ALB, DL, RDL, mark, space, alternating bit, S1 pattern generation and detection

- CMOS technology for low power consumption (typically 100 mW @ 5 V) with power-down mode (15 mW @ 5 V)

- TTL and CMOS compatible inputs and outputs

## FUNCTIONAL DESCRIPTION

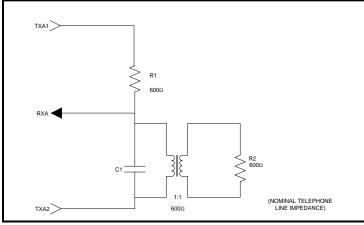

#### HYBRID AND RELAY DRIVER

To make designs more cost effective and space efficient, the 73K224BL includes the 2-wire to 4-wire hybrid with sufficient drive to interface directly to the telecom coupling transformers. In addition, an off hook relay driver with 30mA drive capability is also included to allow use of commonly available mechanical telecom relays.

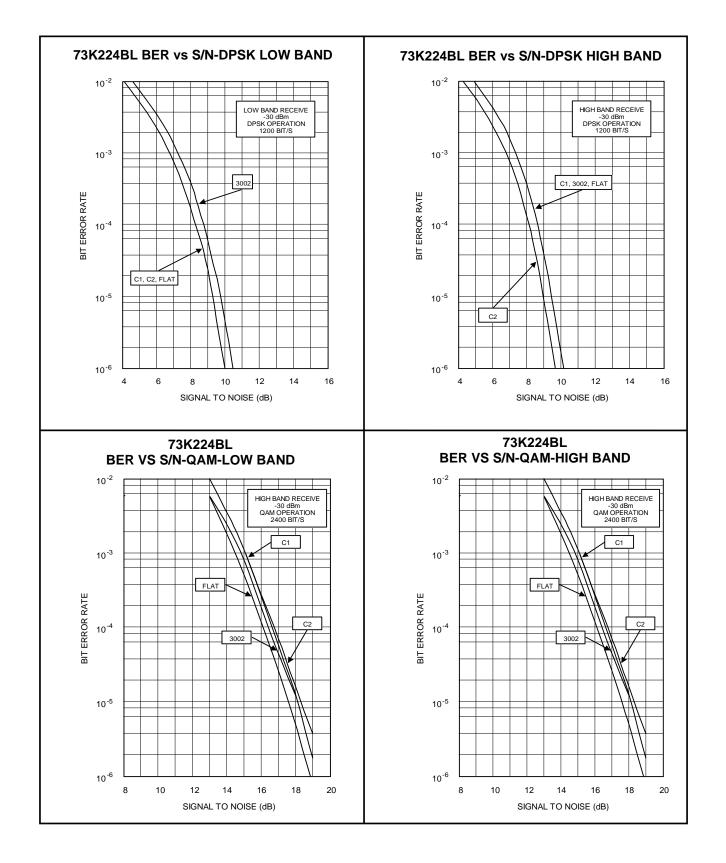

#### QAM MODULATOR/DEMODULATOR

The 73K224BL encodes incoming data into quad-bits represented by 16 possible signal points with specific phase and amplitude levels. The base-band signal is then filtered to reduce intersymbol interference on the band limited telephone network. The modulator transmits this encoded data using either a 1200 Hz (originate mode) or 2400 Hz (answer mode) carrier. The demodulator, although more complex, essentially reverses this procedure while also recovering the data clock from the incoming signal. Adaptive equalization corrects for varying line conditions by automatically changing filter parameters to compensate for line characteristics.

#### DPSK MODULATOR/DEMODULATOR

The 73K224BL modulates a serial bit stream into di-bit pairs that are represented by four possible phase

shifts as prescribed by the Bell 212A/V.22 standards. The base-band signal is then filtered to reduce intersymbol interference on the bandlimited 2-wire PSTN line. Transmission occurs on either a 1200 Hz (originate mode) or 2400 Hz carrier (answer mode). Demodulation is the reverse of the modulation process, with the incoming analog signal eventually decoded into di-bits and converted back to a serial bit stream. The demodulator also recovers the clock, which was encoded into the analog signal during modulation. Demodulation occurs using either a 1200 Hz carrier (answer mode or ALB originate mode) or a 2400 Hz carrier (originate mode or ALB answer mode). Adaptive equalization is also used in DPSK modes for optimum operation with varying line conditions.

#### FSK MODULATOR/DEMODULATOR

The FSK modulator produces a frequency modulated analog output signal using two discrete frequencies to represent the binary data. The Bell 103 standard frequencies of 1270 and 1070 Hz

## FUNCTIONAL DESCRIPTION (continued)

(originate mark and space) and 2225 and 2025 Hz (answer mark and space) are used when this mode is selected. V.21 mode uses 980 and 1180 Hz (originate, mark and space) or 1650 and 1850

Hz (answer, mark and space). Demodulation involves detecting the received frequencies and decoding them into the appropriate binary value. The rate converter and scrambler/descrambler are automatically bypassed in the FSK modes.

#### PASSBAND FILTERS AND EQUALIZERS

High and low band filters are included to shape the amplitude and phase response of the transmit and receive signals and provide compromise delay equalization and rejection of out-of-band signals. Amplitude and phase equalization are necessary to compensate for distortion of the transmission line and to reduce intersymbol interference in the band limited receive signal. The transmit signal filtering corresponds to a 75% square root of raised Cosine frequency response characteristic.

#### **ASYNCHRONOUS MODE**

The asynchronous mode is used for communication with asynchronous terminals which may communicate at 600,1200, or 2400 bit/s +1%, -2.5% even though the modem's output is limited to the nominal bit rate ±.01% in DPSK and QAM modes. When transmitting in this mode the serial data on the TXD input is passed through a rate converter which inserts or deletes stop bits in the serial bit stream in order to output a signal that is the nominal bit rate ±.01%. This signal is then routed to a data scrambler and into the analog modulator where quad-bit/di-bit encoding results in the output signal. Both the rate converter and scrambler can be bypassed for handshaking, and synchronous operation as selected. Received data is processed in a similar fashion except that the rate converter now acts to reinsert any deleted stop bits and output data to the terminal at no greater than the bit rate plus 1%. An incoming break signal (low through two characters) will be passed through without incorrectly inserting a stop bit.

## DATA SHEET

The synch/asynch converter also has an extended overspeed mode, which allows selection of an output overspeed range of either +1% or +2.3%. In the extended overspeed mode, stop bits are output at 7/8 rising edge of TXCLK the normal width.

Both the synch/asynch rate converter and the data descrambler are automatically bypassed in the FSK modes.

#### SYNCHRONOUS MODE

Synchronous operation is possible only in the QAM or DPSK modes. Operation is similar to that of the asynchronous mode except that data must be synchronized to a provided clock and no variation in data transfer rate is allowable. Serial input data appearing at TXD must be valid on the rising edge of TXCLK.

TXCLK is an internally derived 1200 or 2400 Hz signal in internal mode and is connected internally to the RXCLK pin in slave mode. Receive data at the RXD pin is clocked out on the falling edge of RXCLK. The asynch/synch converter is bypassed when synchronous mode is selected and data is transmitted at the same rate as it is input.

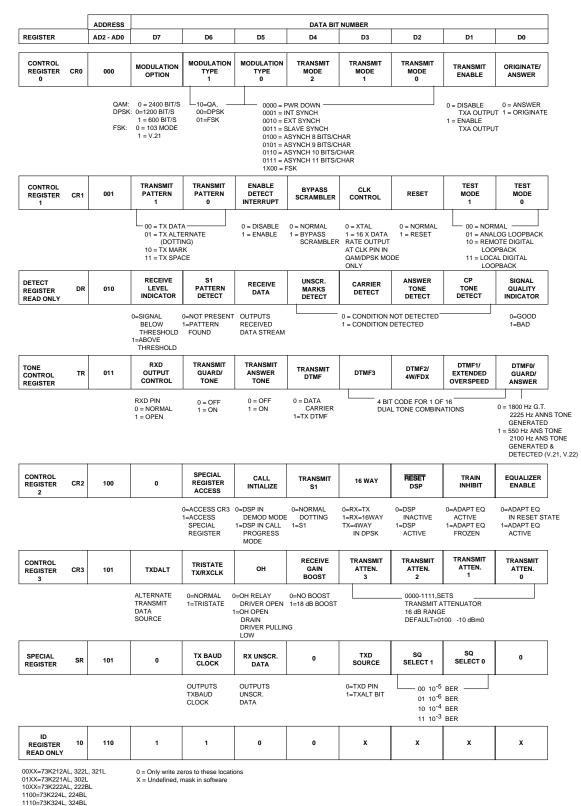

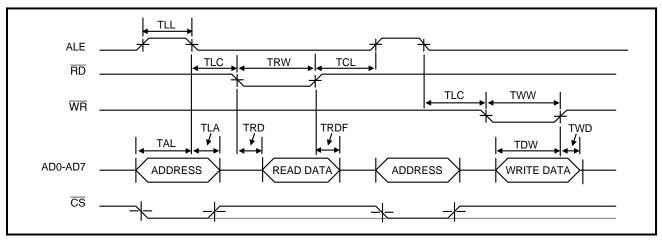

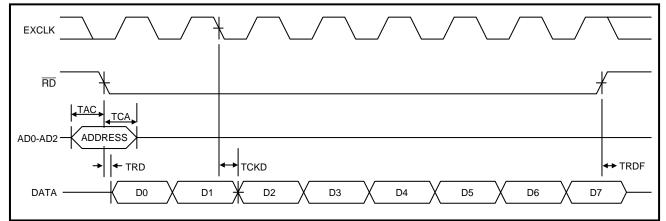

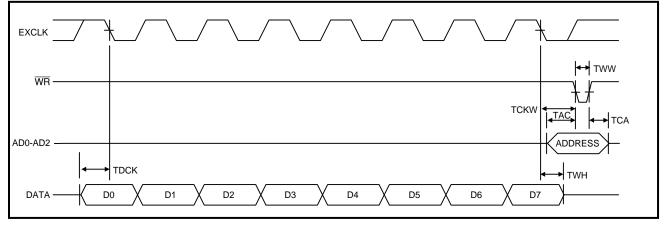

#### PARALLEL BUS CONTROL INTERFACE MODE

Eight 8-bit registers are provided for control, option select, and status monitoring. These registers are addressed with the AD0, AD1, and AD2 multiplexed address lines (latched by ALE) and appear to a control microprocessor as seven consecutive memory locations. Six control registers are read/write memory. The detect and ID registers are read only and cannot be modified except by modem response to monitored parameters.

#### SERIAL CONTROL INTERFACE MODE

The serial Command mode allows access to the 73K224BL control and status registers via a serial control port. In this mode the AD0, AD1, and AD2 lines provide register addresses for data passed through the AD7 (DATA) pin under control of the RD and WR lines. A read operation is initiated when the RD line is taken low. The next eight cycles of EXCLK will then transfer out eight bits of the selected address location LSB first. A write takes place by shifting in eight bits of data LSB first for eight consecutive cycles of EXCLK. WR is then pulsed low and data transfer into the selected register occurs on the rising edge of WR.

#### DTMF GENERATOR

The DTMF generator controls the sending of the sixteen standard DTMF tone pairs. The tone pair sent is determined by selecting transmit DTMF (bit D4) and the 4 DTMF bits (D0-D3) of the Tone Register. Transmission of DTMF tones from TXA is gated by the transmit enable bit of CR0 (bit D1) as with all other analog signals.

## **PIN DESCRIPTION**

## POWER

| NAME | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                |

|------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND  | 1   | I    | System ground                                                                                                                                                                                              |

| VDD  | 16  | I    | Power supply input, 5 V ±10% (73K224BL). Bypass with 0.1 and 22 $\mu F$ capacitors to GND.                                                                                                                 |

| VREF | 31  | 0    | An internally generated reference voltage. Bypass with 0.1 $\mu\text{F}$ capacitor to ground.                                                                                                              |

| ISET | 28  | I    | Chip current reference. Sets bias current for op-amps. The chip current is set by connecting this pin to VDD through a 2 M $\Omega$ resistor. ISET should be bypassed to GND with a 0.1 $\mu$ F capacitor. |

## PARALLEL MICROPROCESSOR CONTROL INTERFACE MODE

| ALE     | 13   | I   | ADDRESS LATCH ENABLE: The falling edge of ALE latches the address on AD0-AD2 and the chip select on CS.                                                                                                                                                                                             |

|---------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0-AD7 | 5-12 | I/O | ADDRESS/DATA BUS: These bi-directional tri-state multiplexed lines carry information to and from the internal registers.                                                                                                                                                                            |

| CS      | 23   | I   | CHIP SELECT: A low on this pin during the falling edge of ALE allows a read cycle or a write cycle to occur. AD0-AD7 will not be driven and no registers will be written if $\overline{CS}$ (latched) is not active. The state of $\overline{CS}$ is latched on the falling edge of ALE.            |

| CLK     | 2    | 0   | OUTPUT CLOCK: This pin is selectable under processor control<br>to be either the crystal frequency (for use as a processor clock) or<br>16 times the data rate for use as a baud rate clock in DPSK<br>modes only. The pin defaults to the crystal frequency on reset.                              |

| ĪNT     | 20   | 0   | INTERRUPT: This open drain output signal is used to inform the processor that a detect flag has occurred. The processor must then read the Detect Register to determine which detect triggered the interrupt. INT will stay low until the processor reads the detect register or does a full reset. |

| RD      | 15   | I   | READ: A low requests a read of the 73K224BL internal registers. Data can not be output unless both $\overline{\text{RD}}$ and the latched $\overline{\text{CS}}$ are active or low.                                                                                                                 |

| RESET   | 30   | I   | RESET: An active high signal on this pin will put the chip into an inactive state. All Control Register bits (CR0, CR1, tone) will be reset. The output of the CLK pin will be set to the crystal frequency. An internal pull-down resistor permits power-on-reset using a capacitor to VDD.        |

## PARALLEL MICROPROCESSOR INTERFACE (continued)

| NAME | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                      |

|------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WR   | 14  | I    | WRITE: A low on this informs the 73K224BL that data is available<br>on AD0-AD7 for writing into an internal register. Data is latched<br>on the rising edge of WR. No data is written unless both WR and<br>the latched $\overline{CS}$ are low. |

#### SERIAL MICROPROCESSOR CONTROL INTERFACE MODE

| NAME       | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD0-AD2    | 5-7 | Ι    | REGISTER ADDRESS SELECTION: These lines carry register addresses and should be valid during any read or write operation.                                                                                                                                                                                                                                                                                                                                                         |

| DATA (AD7) | 12  | I/O  | SERIAL CONTROL DATA: Data for a read/write operation is clocked in or out on the falling edge of the EXCLK pin. The direction of data flow is controlled by the RD pin. RD low outputs data. RD high inputs data.                                                                                                                                                                                                                                                                |

| RD         | 15  | I    | READ: A low on this input informs the 73K224BL that data or status information is being read by the processor. The falling edge of the $\overline{\text{RD}}$ signal will initiate a read from the addressed register. The $\overline{\text{RD}}$ signal must continue for eight falling edges of EXCLK in order to read all eight bits of the referenced register. Read data is provided LSB first. Data will not be output unless the $\overline{\text{RD}}$ signal is active. |

| WR         | 14  | Ι    | WRITE: A low on this input informs the 73K224BL that data or status information has been shifted in through the DATA pin and is available for writing to an internal register. The normal procedure for a write is to shift in data LSB first on the DATA pin for eight consecutive falling edges of EXCLK and then to pulse WR low. Data is written on the rising edge of WR.                                                                                                   |

NOTE: The serial control mode is provided by tying ALE high and  $\overline{CS}$  low. In this configuration AD7 becomes DATA and AD0, AD1 and AD2 become the register address.

## DTE USER

| NAME  | PIN | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXCLK | 22  | I    | EXTERNAL CLOCK: This signal is used in synchronous transmission when the external timing option has been selected. In the external timing mode the rising edge of EXCLK is used to strobe synchronous DPSK transmit data applied to on the TXD pin. Also used for serial control interface.                                                                                                                                                                                                                               |

| RXCLK | 26  | 0    | RECEIVE CLOCK: The falling edge of this clock output is coincident with the transitions in the serial received data output. The rising edge of RXCLK can be used to latch the valid output data. RXCLK will be valid as long as a carrier is present.                                                                                                                                                                                                                                                                     |

| RXD   | 25  | 0    | RECEIVED DATA OUTPUT: Serial receive data is available on<br>this pin. The data is always valid on the rising edge of RXCLK<br>when in synchronous mode. RXD will output constant marks if no<br>carrier is detected.                                                                                                                                                                                                                                                                                                     |

| TXCLK | 21  | 0    | TRANSMIT CLOCK: This signal is used in synchronous<br>transmission to latch serial input data on the TXD pin. Data must<br>be provided so that valid data is available on the rising edge of<br>the TXCLK. The transmit clock is derived from different sources<br>depending upon the synchronization mode selection. In internal<br>mode the clock is generated internally. In external mode TXCLK<br>is phase locked to the EXCLK pin. In slave mode TXCLK is<br>phase locked to the RXCLK pin. TXCLK is always active. |

| TXD   | 24  | Ι    | TRANSMIT DATA INPUT: Serial data for transmission is applied<br>on this pin. In synchronous modes, the data must be valid on the<br>rising edge of the TXCLK clock. In asynchronous modes<br>(1200/600 bit/s or 300 baud) no clocking is necessary. DPSK<br>data must be 1200/600 bit/s +1%, -2.5% or +2.3%, -2.5 % in<br>extended over speed mode.                                                                                                                                                                       |

.

# **PIN DESCRIPTION** (continued)

#### ANALOG INTERFACE AND OSCILLATOR

| NAME        | PIN     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                              |

|-------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXA         | 32      | Ι    | Received modulated analog signal input from the telephone line interface.                                                                                                                                                                                                                                                                |

| TXA1 / TXA2 | 18 / 17 | 0    | Transmit Analog (differential outputs): These pins provide the<br>analog output signals to be transmitted to the telephone line. The<br>drivers will differentially drive the impedance of the line<br>transformer and the line matching resistor. An external hybrid can<br>also be built using TXA1 as a single ended transmit signal. |

| XTL1 / XTL2 | 3 / 4   | Ι    | These pins are for the internal crystal oscillator requiring a 11.0592 MHz parallel mode crystal. Load capacitors should be connected from XTL1 and XTL2 to ground. XTL2 can also be driven from an external clock.                                                                                                                      |

| OH          | 27      | 0    | OFF-HOOK RELAY DRIVER: This signal is an open drain output capable of sinking 30mA and is used for controlling a relay. The output is the complement of the OH register bit in the ID Register.                                                                                                                                          |

#### **REGISTER ADDRESS TABLE**

## **CONTROL REGISTER 0**

| CR0         | D7               | D6                   | D5               |                                                                                                                                                                                                                            | D4                                                                      | D3                                                                | D2                             | D1                 | D0                                                       |  |

|-------------|------------------|----------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------|--------------------|----------------------------------------------------------|--|

| ADDR<br>000 | MODUL.<br>OPTION | MODUL.<br>TYPE 1     | MODUL.<br>TYPE 0 |                                                                                                                                                                                                                            | NSMIT                                                                   | TRANSMIT<br>MODE 1                                                | TRANSMIT<br>MODE 0             | TRANSMIT<br>ENABLE | ANSWER/<br>ORIGINATE                                     |  |

| BIT         |                  | NAME                 | CO               | DITIC                                                                                                                                                                                                                      | ON                                                                      | DESCRIPTION                                                       | I                              |                    |                                                          |  |

| D0          |                  | Answer/<br>Originate |                  | 0                                                                                                                                                                                                                          |                                                                         | Selects answer mode (transmit in high band, receive in low band). |                                |                    |                                                          |  |

|             |                  |                      |                  | 1                                                                                                                                                                                                                          |                                                                         | high band).                                                       | , ,                            |                    | oand, receive in                                         |  |

| D1          |                  | Transmit             |                  | 0                                                                                                                                                                                                                          |                                                                         | Disables transr                                                   |                                |                    |                                                          |  |

|             |                  | Enable               |                  | 1                                                                                                                                                                                                                          |                                                                         | Enables transm                                                    |                                |                    |                                                          |  |

|             |                  |                      |                  |                                                                                                                                                                                                                            | Note: Transmit enable must be set to 1 to allow of answer tone or DTMF. |                                                                   |                                | allow activation   |                                                          |  |

| D5,D4       |                  | Transmit             | D5 E             | 04 D3                                                                                                                                                                                                                      | D2                                                                      |                                                                   |                                |                    |                                                          |  |

| D3,D2       |                  | Mode                 | 0 (              | ) ()                                                                                                                                                                                                                       | 0                                                                       | Selects Power digital interface                                   |                                | All functions      | disabled except                                          |  |

|             |                  |                      | 0 (              | 0 0 1 Internal synchronous mode in this mode TXC<br>internally derived 600,1200 or 2400 Hz signal. S<br>data appearing at TXD must be valid on the risir<br>TXCLK. Receive data is clocked out of RXD on<br>edge of RXCLK. |                                                                         |                                                                   |                                |                    | nal. Serial input<br>ie rising edge of                   |  |

|             |                  |                      | 0 (              | ) 1                                                                                                                                                                                                                        | 0                                                                       | internal synchro                                                  | onous, but TX<br>nd a 600, 120 | CLK is conned      | is identical to<br>cted internally to<br>c clock must be |  |

|             |                  |                      | 0                | ) 1                                                                                                                                                                                                                        | 1                                                                       |                                                                   | nodes TXCLK                    |                    | ation as other<br>internally to the                      |  |

|             |                  |                      | 0 1              | 0                                                                                                                                                                                                                          | 0                                                                       | Selects a sync<br>data bits, 1 stop                               |                                | 8 bits/charac      | ter (1 start bit, 6                                      |  |

|             |                  |                      | 0 1              | 0                                                                                                                                                                                                                          | 1                                                                       | Selects asynch data bits, 1 stop                                  |                                | - 9 bits/charac    | ter (1 start bit, 7                                      |  |

|             |                  |                      | 0                | 1                                                                                                                                                                                                                          | 0                                                                       | Selects asynch<br>8 data bits, 1 st                               |                                | - 10 bits/chara    | acter (1 start bit,                                      |  |

|             |                  |                      | 0 ~              | -                                                                                                                                                                                                                          | 1                                                                       | 8 data bits, 1 st                                                 | top bit) or 2 sto              |                    | acter (1 start bit,                                      |  |

|             |                  |                      | 1 2              | K 0                                                                                                                                                                                                                        | 0                                                                       | Selects FSK op                                                    | peration.                      |                    |                                                          |  |

| D6,D5       | Ν                | Iodulation<br>Type   |                  | D6 D5<br>1 0                                                                                                                                                                                                               |                                                                         | QAM                                                               |                                |                    |                                                          |  |

|             |                  | iyhe                 | (                |                                                                                                                                                                                                                            |                                                                         | DPSK                                                              |                                |                    |                                                          |  |

|             |                  |                      |                  | ) 1                                                                                                                                                                                                                        |                                                                         | FSK                                                               |                                |                    |                                                          |  |

## CONTROL REGISTER 0 (continued)

| CR0         | D          | 7 | D6                   | D5               | D4                 | D3                            | D2                 | D1                 | D0                   |  |  |

|-------------|------------|---|----------------------|------------------|--------------------|-------------------------------|--------------------|--------------------|----------------------|--|--|

| ADDR<br>000 | MOD<br>OPT |   | MODUL.<br>TYPE 1     | MODUL.<br>TYPE 0 | TRANSMIT<br>MODE 2 | TRANSMIT<br>MODE 1            | TRANSMIT<br>MODE 0 | TRANSMIT<br>ENABLE | ANSWER/<br>ORIGINATE |  |  |

| BIT         |            |   | NAME                 | CON              | IDITION            | DESCRIPTION                   |                    |                    |                      |  |  |

| D7          |            | N | lodulation<br>Option |                  | 0                  | QAM selects 24 selects 103 mo |                    | K selects 1200     | ) bit/s. FSK         |  |  |

|             |            |   |                      |                  | 1                  | DPSK selects 600 bit/s.       |                    |                    |                      |  |  |

|             |            |   |                      |                  |                    | FSK selects V.21 mode.        |                    |                    |                      |  |  |

## **CONTROL REGISTER 1**

| CR1         | D7                  |               | D6                      |     | D5                          | D4                                                                                                              | D3                                            | D2                     | D1                         | D0                                                             |  |

|-------------|---------------------|---------------|-------------------------|-----|-----------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------|----------------------------|----------------------------------------------------------------|--|

| ADDR<br>001 | TRANS<br>PATTE<br>1 |               | TRANSMI<br>PATTERI<br>0 | N I | ENABLE<br>DETECT<br>FERRUPT | BYPASS<br>SCRAMBLER                                                                                             | CLOCK<br>CONTROL                              | RESET                  | TEST<br>MODE 1             | TEST<br>MODE 0                                                 |  |

| BIT         |                     | N             | AME                     | CO  | NDITION                     | DESCRIPTIC                                                                                                      | ON                                            |                        |                            |                                                                |  |

| D0, D1      |                     | Test          | Mode                    | 0   | 1 D0                        |                                                                                                                 |                                               |                        |                            |                                                                |  |

|             |                     |               |                         |     | 0 0                         | Selects norm                                                                                                    | al operating                                  | mode                   |                            |                                                                |  |

|             |                     |               |                         |     | 0 1                         | signal back to<br>the same car                                                                                  | o the receive<br>rier frequen<br>transmit ena | r, and ca<br>cy as the | uses the re<br>transmitter | hitted analog<br>ceiver to use<br>. To squelch<br>one Register |  |

|             |                     |               |                         |     | 1 0                         |                                                                                                                 | smit data int                                 | ernally, a             |                            | ata is looped<br>s forced to a                                 |  |

|             |                     |               |                         |     | 1 1                         | Selects local digital loopback. Internally loops TXD back RXD and continues to transmit data carrier at TXA pin |                                               |                        |                            |                                                                |  |

| D2          |                     | R             | eset                    |     | 0                           | Selects Norm                                                                                                    | Selects Normal Operations                     |                        |                            |                                                                |  |

|             |                     |               |                         | 1   |                             | bits (CR0, C                                                                                                    | CR1, CR2, C<br>bit D2. The                    | R3 and                 | tone) are i                | ntrol Register<br>reset to zero<br>bin will be set             |  |

| D3          | (                   | Clock Control |                         |     | 0                           | Selects 11.05                                                                                                   | 592 MHz crys                                  | stal echo o            | output at Cl               | LK pin                                                         |  |

|             |                     |               |                         |     | 1                           | Selects 16<br>DPSK/QAM                                                                                          |                                               | ata rate               | output at                  | CLK pin in                                                     |  |

#### CONTROL REGISTER 1 (continued)

| CR1         | [ | 70                         | D6                      | [     | 05                    | D4                                            | D3                                                                                           | D2                                                | D1                                      | D0                                                                           |  |

|-------------|---|----------------------------|-------------------------|-------|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------|--|

| ADDR<br>001 |   | NSMIT<br>TERN<br>1         | TRANSMI<br>PATTERN<br>0 | N DET | ABLE<br>TECT<br>RRUPT | BYPASS<br>SCRAMBLER                           | CLOCK<br>CONTROL                                                                             | RESET                                             | TEST<br>MODE 1                          | TEST<br>MODE 0                                                               |  |

| BIT         |   | N                          | AME                     | COND  | ITION                 | DESCRIPTIC                                    | DN                                                                                           |                                                   |                                         |                                                                              |  |

| D4          |   | Bypass<br>Scrambler        |                         | (     | )                     | Selects norm through scrar                    |                                                                                              | DPSK a                                            | ind QAM d                               | ata is passed                                                                |  |

|             |   |                            |                         |       | 1                     |                                               | Selects Scrambler bypass. Bypass DPSK and QA is route around scrambler in the transmit path. |                                                   |                                         |                                                                              |  |

| D5          |   | Enable Detect<br>Interrupt |                         | (     | )                     |                                               | Disables interrupt at INT pin. All interrup disabled in power-down mode.                     |                                                   |                                         |                                                                              |  |

|             |   |                            |                         |       | 1                     | change in sta<br>tone and call<br>the TX enab | atus of DR b<br>I progress de<br>le bit is set.<br>activated. Al                             | its D1- D<br>etect inter<br>Carrier<br>I interrup | 4 and D6.<br>rupts are r<br>detect is n | erated with a<br>The answer<br>nasked when<br>nasked when<br>lisabled if the |  |

|             |   |                            |                         | D7    | D6                    |                                               |                                                                                              |                                                   |                                         |                                                                              |  |

| D6, D7      |   | Transmit<br>Pattern        |                         | 0     | 0                     | Selects norm<br>of the TXD pi                 |                                                                                              | mission a                                         | s controlle                             | d by the state                                                               |  |

|             |   |                            |                         |       |                       | 0                                             | 1                                                                                            |                                                   | ng and hands                            | haking.                                                                      |  |

|             |   |                            |                         | 1     | 0                     | Selects a cor                                 | Selects a constant mark transmit pattern.                                                    |                                                   |                                         |                                                                              |  |

|             |   |                            |                         | 1     | 1                     | Selects a cor                                 | nstant space                                                                                 | transmit p                                        | attern.                                 |                                                                              |  |

#### DETECT REGISTER

| DR          |    | D7                     | D6                      | D5           |  | D4                                                                                                             | D3              | D2                        | D1                      | D0                                    |

|-------------|----|------------------------|-------------------------|--------------|--|----------------------------------------------------------------------------------------------------------------|-----------------|---------------------------|-------------------------|---------------------------------------|

| ADDR<br>010 | LE | CEIVE<br>EVEL<br>CATOR | S1<br>PATTERN<br>DETECT | N DATA N     |  | NSCR.<br>MARK<br>ETECT                                                                                         | CARR.<br>DETECT | ANSWER<br>TONES<br>DETECT | CALL<br>PROG.<br>DETECT | SIGNAL<br>QUALITY<br>INDICATOR        |

| BIT         |    | NAME                   |                         | CONDITION DE |  | DESC                                                                                                           | RIPTION         |                           |                         |                                       |

| D0          |    | Signal Quality         |                         | 0            |  | Indicates normal received signal.                                                                              |                 |                           |                         |                                       |

|             |    | Indi                   | cator                   | 1            |  | Indicates low received signal quality (above average error rate). Interacts with Special Register bits D2, D1. |                 |                           |                         |                                       |

| D1          |    | Call Progress          |                         | 0            |  | No call progress tone detected.                                                                                |                 |                           |                         |                                       |

|             |    | Detect                 |                         | 1            |  | detecti                                                                                                        | on circuitry    |                           | by energy ir            | The call progress<br>n the normal 350 |

| DETECT REGISTER | (continued) |

|-----------------|-------------|

|-----------------|-------------|

| DR          | [  | 07                                                                                                                                                                 | D6                     | D5        | [ | D4                                                                                                   | D3                                        | D2                             | D1                                        | D0                                                                          |  |  |

|-------------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------|---|------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------|-------------------------------------------|-----------------------------------------------------------------------------|--|--|

| ADDR<br>010 | LE | EIVE<br>VEL<br>CATOR                                                                                                                                               | S1<br>PATTER<br>DETECI |           | M | ISCR.<br>ARK<br>TECT                                                                                 | CARR.<br>DETECT                           | ANSWER<br>TONES<br>DETECT      | CALL<br>PROG.<br>DETECT                   | SIGNAL<br>QUALITY<br>INDICATOR                                              |  |  |

| BIT         |    | NA                                                                                                                                                                 | ME                     | CONDITION |   | DESCRIPTION                                                                                          |                                           |                                |                                           |                                                                             |  |  |

| D2          |    | Answe                                                                                                                                                              | er Tone                | 0         |   | No ans                                                                                               | swer tone de                              | etected.                       |                                           |                                                                             |  |  |

|             |    | Rec                                                                                                                                                                | eived                  | 1         |   | tone in<br>mode<br>mode f                                                                            | Bell mode<br>(TR bit D0<br>for detection  | (TR bit D0<br>= 1). The        | = 0) or 210<br>device mus<br>tone. Both a | 2225 Hz answer<br>0 Hz if in CCITT<br>t be in originate<br>answer tones are |  |  |

| D3          |    | Carrie                                                                                                                                                             | r Detect               | 0         |   | No car                                                                                               | rier detecte                              | d in the recei                 | ve channel.                               |                                                                             |  |  |

|             |    |                                                                                                                                                                    |                        | 1         |   | Indicated carrier has been detected in the recei channel.                                            |                                           |                                |                                           |                                                                             |  |  |

| D4          |    | Unscrambled                                                                                                                                                        |                        | 0         |   | No uns                                                                                               | scrambled n                               | nark.                          |                                           |                                                                             |  |  |

|             |    | Mark                                                                                                                                                               | Detect                 | 1         |   |                                                                                                      |                                           | n of unscrar<br>ne qualified l |                                           | s in the received                                                           |  |  |

| D5          |    | Recei                                                                                                                                                              | ve Data                |           |   | the sa                                                                                               | me as that                                |                                | the RXD p                                 | eam. This data is<br>bin, but it is not                                     |  |  |

| D6          |    | S1 P                                                                                                                                                               | attern                 | 0         |   | No S1                                                                                                | pattern beir                              | ng received.                   |                                           |                                                                             |  |  |

|             |    | Detect 1 S1 pattern detected. Should be time q<br>S1 pattern is defined as a doubl<br>unscrambled 1200 bit/s DPSK signa<br>aligned with baud clock to be detected. |                        |           |   | a double<br>SK signal. I                                                                             | le di-bit (001100)<br>al. Pattern must be |                                |                                           |                                                                             |  |  |

| D7          |    |                                                                                                                                                                    | /e Level<br>cator      | 0         |   | Received signal level below threshold, (typical $\approx$ -25 c can use receive gain boost (+18 dB). |                                           |                                |                                           |                                                                             |  |  |

|             |    |                                                                                                                                                                    |                        | 1         |   | Receiv                                                                                               | ed signal al                              | bove thresho                   | ld.                                       |                                                                             |  |  |

#### TONE REGISTER

| TR          | D7         |                         | D6                |    | D                          | 5    |          | D4                                                    | D3                                                             | D2                                                       | D1                                                                                                       | D0                                                                 |  |  |

|-------------|------------|-------------------------|-------------------|----|----------------------------|------|----------|-------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

| ADDR<br>011 |            | OUTPUT<br>CONTROL GUARI |                   |    | TRANSMIT<br>ANSWER<br>TONE |      |          | FRANSMIT<br>DTMF                                      | DTMF 3                                                         | DTMF 2/<br>4-WIRE<br>FDX                                 | DTMF 1/<br>EXTENDED<br>OVER-<br>SPEED                                                                    | DTMF 0/<br>ANSWER<br>GUARD                                         |  |  |

| BIT         |            | Ν                       | AME               | C  | OND                        | ITIO | N        | DESCRIPTION                                           |                                                                |                                                          |                                                                                                          |                                                                    |  |  |

|             |            |                         |                   | D6 | D5                         | D4   | D0       | D0 intera                                             | D0 interacts with bits D6, D5, and D4 as shown                 |                                                          |                                                                                                          |                                                                    |  |  |

| D0          |            | MF 0/                   | Х                 | Х  | 1                          | Х    | Transmit | Transmit DTMF tones must be in DPSK or Bell 103 mode. |                                                                |                                                          |                                                                                                          |                                                                    |  |  |

|             |            |                         | nswer/<br>rd Tone | Х  | 1                          | 0    | 0        |                                                       | Select Bell mode answer tone. Interacts with DR bit TR bit D5. |                                                          |                                                                                                          |                                                                    |  |  |

|             |            |                         |                   | Х  | 1                          | 0    | 1        | Select C<br>and TR b                                  |                                                                | e answer to                                              | one. Interacts w                                                                                         | vith DR bit D2                                                     |  |  |

|             |            |                         |                   | 1  | 0                          | 0    | 0        | Select 18                                             | 300 Hz gua                                                     | rd tone.                                                 |                                                                                                          |                                                                    |  |  |

|             |            |                         |                   | 1  | 0                          | 0    | 1        | Select 5                                              | Select 550 Hz guard tone.                                      |                                                          |                                                                                                          |                                                                    |  |  |

|             |            |                         |                   |    | D4                         | D1   |          | D1 interacts with D4 as shown.                        |                                                                |                                                          |                                                                                                          |                                                                    |  |  |

| D1          |            | DT                      | MF 1/             |    | 0                          | 0    |          | Asynchro                                              | Asynchronous QAM or DPSK +1% -2.5%. (normal)                   |                                                          |                                                                                                          |                                                                    |  |  |

|             |            |                         | tended<br>erspeed |    | 0                          | 1    |          | Asynchro                                              |                                                                | M or DPS                                                 | K +2.3% -2.5                                                                                             | %. (extended                                                       |  |  |

|             |            |                         |                   |    | D4                         | D2   |          |                                                       |                                                                |                                                          |                                                                                                          |                                                                    |  |  |

| D2          |            | DT                      | MF 2/             |    | 0                          | 0    |          | Selects 2                                             | 2-wire duple                                                   | ex or half du                                            | ıplex                                                                                                    |                                                                    |  |  |

|             | 4 Wire FDX |                         |                   |    | 0                          | 1    |          | selected<br>mode se<br>high or l<br>band as           | . The rece<br>elected by<br>ow band s<br>the receive           | eive path o<br>the ANS/O<br>election. Th<br>er, but does | x in the mod<br>corresponds to<br>RIG bit CR0 D<br>ne transmitter is<br>not have mag<br>in the receive p | the receive<br>of in terms of<br>s in the same<br>nitude filtering |  |  |

#### TONE REGISTER

| TR                | D7                             |    | D6                        |                    | D                  | 5   |    | D4               | D3          | D2                   | D1                                                 | D0                         |  |  |

|-------------------|--------------------------------|----|---------------------------|--------------------|--------------------|-----|----|------------------|-------------|----------------------|----------------------------------------------------|----------------------------|--|--|

| ADDR<br>011       | RXE<br>OUTP<br>CONTF           | TU | TRANSMIT<br>GUARD<br>TONE |                    | RAN<br>ANSV<br>TOI | VER |    | TRANSMIT<br>DTMF | DTMF 3      | DTMF<br>4-WIR<br>FDX | E EXTENDED                                         | DTMF 0/<br>ANSWER<br>GUARD |  |  |

| BIT               |                                | Ν  | AME                       | CONDITION          |                    |     | DN | DESCRI           | DESCRIPTION |                      |                                                    |                            |  |  |

|                   |                                |    |                           |                    |                    |     |    |                  |             | -                    | 5, and D4 as sho                                   |                            |  |  |

| D3, D2,<br>D1, D0 | D3, D2, DTMF 3, D1, D0 2, 1, 0 |    |                           |                    |                    |     |    |                  |             | d TX ena             | he pairs that will t<br>able bit (CR0, bit<br>low: |                            |  |  |

|                   |                                |    |                           | DTMF CODE KEYBOARD |                    |     |    |                  | TON         | ES                   |                                                    |                            |  |  |

|                   |                                |    |                           |                    | D2                 | D1  | D0 | EQL              | JIVALENT    |                      | LOW                                                | HIGH                       |  |  |

|                   |                                |    |                           | 0                  | 0                  | 0   | 1  |                  | 1           |                      | 697                                                | 1209                       |  |  |

|                   |                                |    |                           | 0                  | 0                  | 1   | 0  |                  | 2           |                      | 697                                                | 1336                       |  |  |

|                   |                                |    |                           | 0                  | 0                  | 1   | 1  |                  | 3           |                      | 697                                                | 1477                       |  |  |

|                   |                                |    |                           | 0                  | 1                  | 0   | 0  |                  | 4           |                      | 770                                                | 1209                       |  |  |

|                   |                                |    |                           | 0                  | 1                  | 0   | 1  |                  | 5           |                      | 770                                                | 1336                       |  |  |

|                   |                                |    |                           | 0                  | 1                  | 1   | 0  |                  | 6           |                      | 770                                                | 1477                       |  |  |

|                   |                                |    |                           | 0                  | 1                  | 1   | 1  |                  | 7           |                      | 852                                                | 1209                       |  |  |

|                   |                                |    |                           | 1                  | 0                  | 0   | 0  |                  | 8           |                      | 852                                                | 1336                       |  |  |

|                   |                                |    |                           | 1                  | 0                  | 0   | 1  |                  | 9           |                      | 852                                                | 1477                       |  |  |

|                   |                                |    |                           | 1                  | 0                  | 1   | 0  |                  | 0           |                      | 941                                                | 1336                       |  |  |

|                   |                                |    |                           | 1                  | 0                  | 1   | 1  |                  | *           |                      | 941                                                | 1209                       |  |  |

|                   |                                |    |                           | 1                  | 1                  | 0   | 0  |                  | #           |                      | 941                                                | 1477                       |  |  |

|                   |                                |    |                           | 1                  | 1                  | 0   | 1  |                  | А           |                      | 697                                                | 1633                       |  |  |

|                   |                                |    |                           | 1                  | 1                  | 1   | 0  |                  | В           |                      | 770                                                | 1633                       |  |  |

|                   |                                |    |                           | 1                  | 1                  | 1   | 1  |                  | С           |                      | 852                                                | 1633                       |  |  |

|                   |                                |    |                           | 0                  | 0                  | 0   | 0  |                  | D           |                      | 941                                                | 1633                       |  |  |

| D4                | D4 TX DTMF                     |    |                           |                    | (                  | C   |    | Disable [        | DTMF.       |                      |                                                    |                            |  |  |

|                   | (Transmit<br>DTMF)             |    |                           |                    |                    | 1   |    | continuo         |             | this bit is          | ed DTMF tones a<br>s high. TX DTMF                 |                            |  |  |

NOTE: DTMF0-DTMF2 should be set to an appropriate state after DTMF dialing to avoid unintended operation.

## TONE REGISTER (continued)

| TR          | I   | 07                                          | D6       |                            | D5              |    | D4                                                                                                 | D3                                                                                                                           | D2                                           | D1                                    | D0                         |  |  |

|-------------|-----|---------------------------------------------|----------|----------------------------|-----------------|----|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---------------------------------------|----------------------------|--|--|

| ADDR<br>011 | OU. | RXD TRANSMI<br>OUTPUT GUARD<br>CONTROL TONE |          | TRANSMIT<br>ANSWER<br>TONE |                 | Т  | RANSMIT<br>DTMF                                                                                    | DTMF 3                                                                                                                       | DTMF 2/<br>4-WIRE<br>FDX                     | DTMF 1/<br>EXTENDED<br>OVER-<br>SPEED | DTMF 0/<br>ANSWER<br>GUARD |  |  |

| BIT         |     | N                                           | AME      | CO                         | NDITIO          | N  | DESCRIPTION                                                                                        |                                                                                                                              |                                              |                                       |                            |  |  |

|             |     |                                             |          | D5                         | D4              | D0 | with DR                                                                                            | D5 interacts with bits D4 and D0 as shown. Also interact with DR bit D2 in originate mode (see Detect Register description). |                                              |                                       |                            |  |  |

| D5          |     | Tra                                         | ansmit   | 0                          | 0               | Х  | Disables                                                                                           | Disables answer tone generator.                                                                                              |                                              |                                       |                            |  |  |

|             |     | Ansv                                        | ver Tone | 1                          | 0               | 0  | In answer mode, a Bell 2225 Hz tone is transmost continuously when the transmit enable bit is set. |                                                                                                                              |                                              |                                       |                            |  |  |

|             |     |                                             |          | 1                          | 0               | 1  | Likewise                                                                                           | , a CCITT :                                                                                                                  | 2100 Hz an                                   | swer tone is tra                      | insmitted.                 |  |  |